I design and deliver hardware systems that perform, from first schematic to lab-validated product, while leading teams to execute with clarity and speed.

Hi there!

I’m Diana

About

Highlights

Experience

Radio Systems Co-Lead

- Defined radio system architecture for LoRa telemetry redesign, coordinating hardware–firmware–test integration on a race-critical timeline.

- Executed PCB design and bring-up of STM32WL-based RF link, achieving 2 km validated range and ~30% fewer sequencing failures via standardized debug flows.

FPGA Design — Embedded AV Systems

- Led research track & design reviews; aligned RTL, testbench, and synth owners; hit timing at 100 MHz with <10% LUT, <5% BRAM.

- Automated Quartus synth & ModelSim runs with Tcl/Bash (deterministic one-command builds); structured verification with focused benches and pass/fail artifacts.

Projects

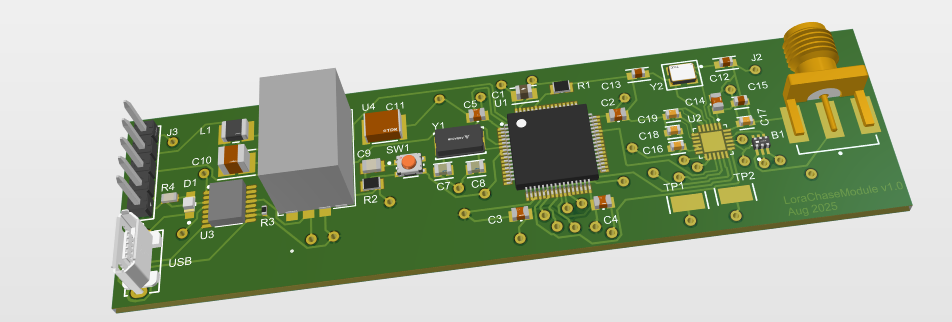

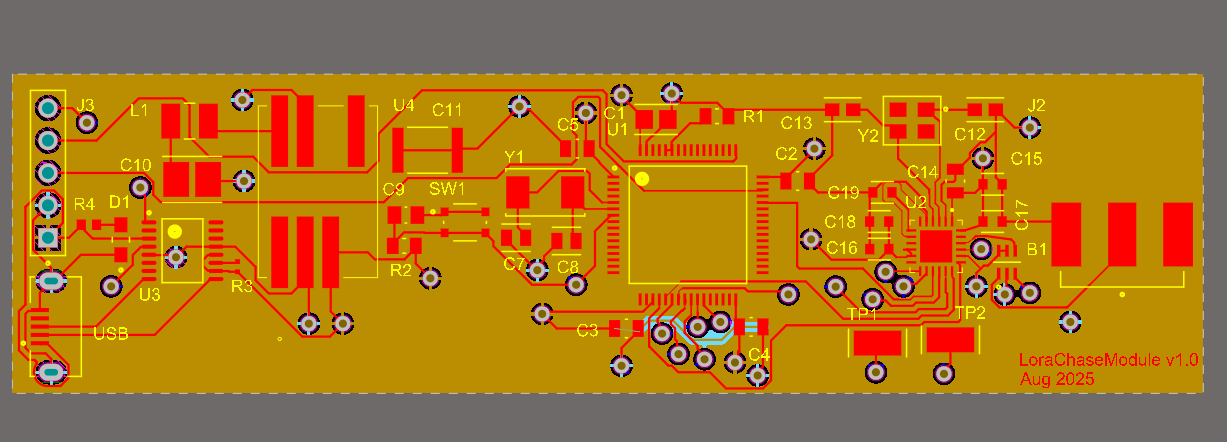

LoRa Telemetry Module

Chase & car modules with live data routing to the vehicle network. Clean packet design and scope-verified performance.

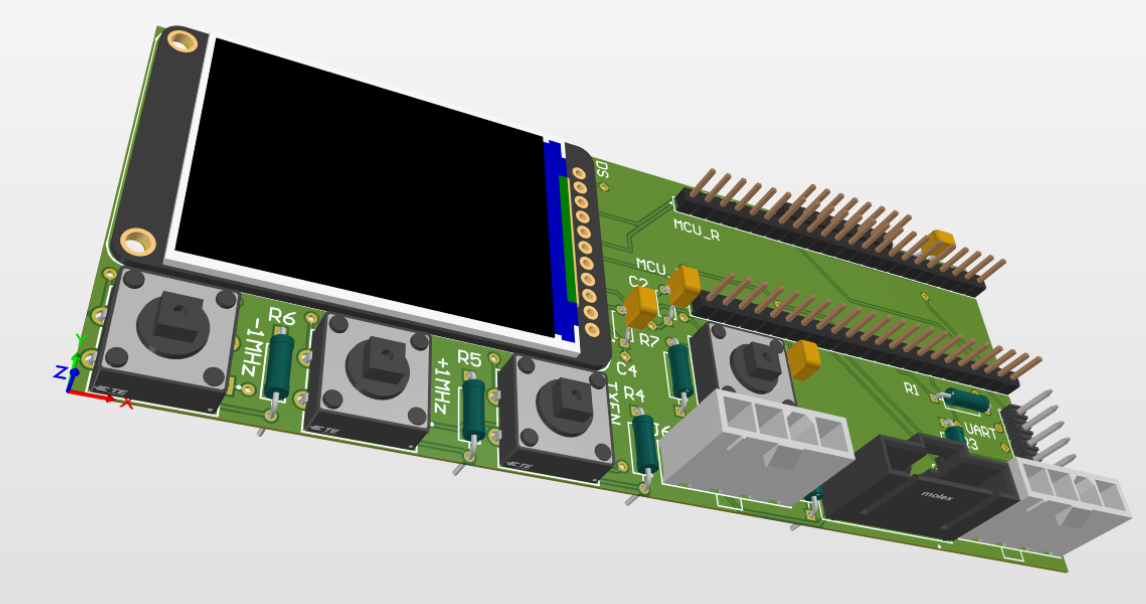

SDR Controller Hardware

LO generation & RX/TX switching with ±1 kHz stability and accurate 90° I/Q. Firmware + Python automation for validation.

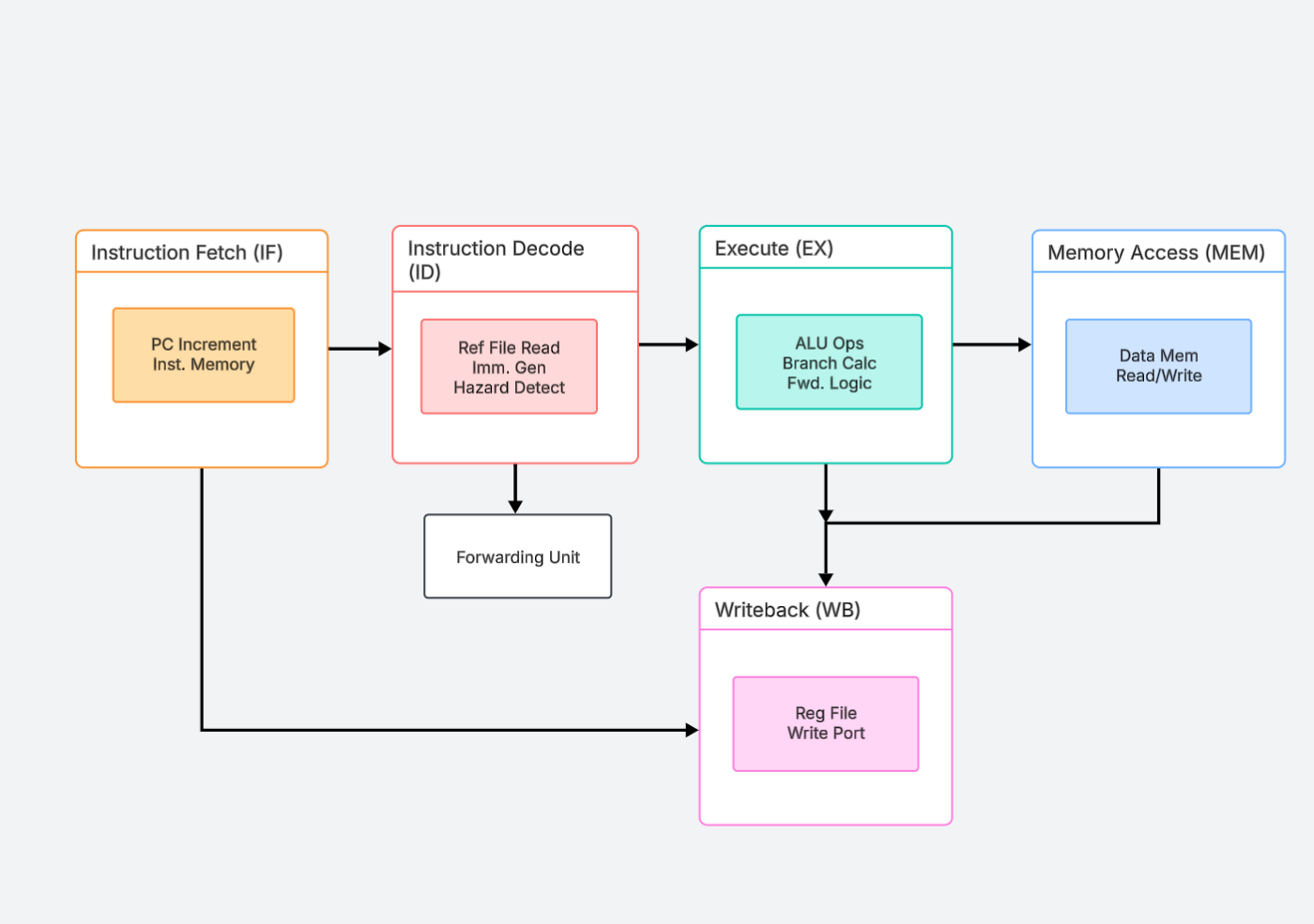

RISC-V 5-Stage Pipelined CPU

Synthesizable CPU with coverage-driven verification. Tcl-driven regressions and waveform triage accelerate iteration.

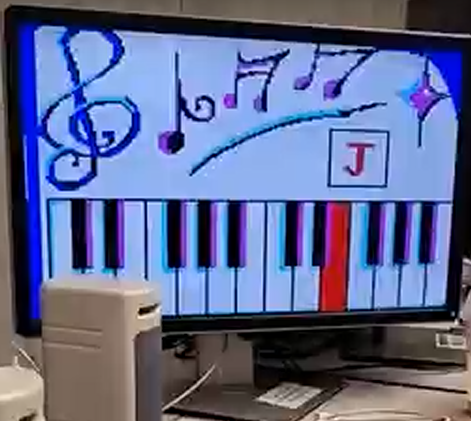

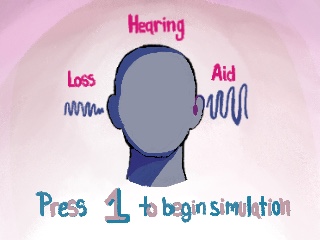

FPGA Nios® V Hearing Loss & Aid Simulator

Real-time DSP on DE1-SoC with VGA UI and PS/2 controls. Measured latency & behavior match design goals.

Skills

Leadership

Guiding cross-functional teams to hit aggressive timelines with clarity, accountability, and momentum.

PCB Design

Stackup planning, impedance, pours, placement & routing, DRC, bring-up.

FPGA / RTL

Verilog/SystemVerilog, timing closure, verification, clean build flows.

Embedded Systems

STM32 (HAL), drivers, packets/CRC, USB-CDC, tooling & test harnesses.

Mixed-Signal & Analog

Filters, sampling paths, power integrity awareness, measurement.

ASIC Design & Verification

Coverage-driven benches, hazards/forwarding, scripted regressions.

Extracurriculars

Strategy & Operations Lead

Redesigned selection and role guides to scale reliably for a global hackathon.

Operations & Training Lead

Built and delivered a cohesive program across live sessions and an online course.

Co-VP Competitions

Launched a realistic case competition in power, climate, and logistics.

Student Mentor

Ran approachable workshops; partnered with Blue Sky Solar Racing on energy topics.